Intel-Xeons künftig auch mit schnellem HBM-Speicher

Die nächste Xeon-SP-Generation Sapphire Rapids bringt Varianten mit HBM; schnelle Ethernet-Adapter und -Switches sollen Infiniband pleonastisch zeugen.

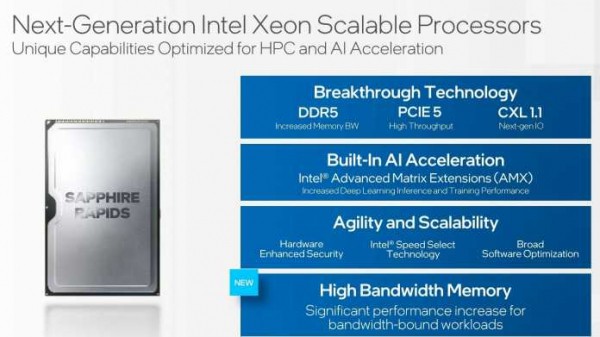

Intels vierte Xeon-SP-Generation „Sapphire Rapids“ bringt viele neue Funktionen.

(Bild: Intel)

c’t Magazin Von

- Christof Windeck

Anlässlich der Supercomputer-Konferenz ISC 2021 bestätigt Intel, Xeon-SP-Prozessoren der vierten Generation Sapphire Rapids auch in Modellversionen mit integriertem High Bandwidth Memory (HBM) auszuliefern. Als HBM bezeichnet man gestapelte SDRAM-Chips mit sehr vielen Signalleitungen für extrem hohe Datentransferleistungen. Mit dem aktuellen Typ HBM2E erzielt etwa die Nvidia A100 über 2 TByte/s. Acht DDR5-4800-Kanäle mit je 38,4 GByte/s schaffen hingegen zusammen "nur" rund 300 GByte/s und haben höhere Latenzen.

Intel verrät bisher allerdings weder die Kapazität noch den Typ des HBM-Speichers auf den kommenden Xeons; laut Spekulationen sollen es bis zu 64 GByte HBM2E sein. Auch Preise und Leistungsaufnahmeklassen sind bisher unbekannt; man munkelt von TDP-Werten bis 350 Watt.

Intel stellt aber klar, dass es die HBM-Xeons nicht nur für Supercomputer-Projekte und Sonderkunden geben soll, sondern auch im normalen Lieferprogramm. Zudem können die HBM-Xeons gleichzeitig "normalen" DDR5-Arbeitsspeicher ansteuern, können aber auch ohne externes RAM laufen.

Für Supercomputer schon gebucht

Die Sapphire-Rapids-Xeons aus der 10-Nanometer-Fertigung und die aus über 40 Chips zusammengefügten "Ponte Vecchio"-Rechenbeschleuniger sind für Intel extrem wichtige Produkte und schon für mehrere Supercomputer eingeplant. Herausragendes Projekt ist das 500 Millionen US-Dollar teure Exaflops-System Aurora am Argonne National Lab; aber auch der bayrische SuperMUC-NG Phase 2 soll dank Sapphire Rapids und Ponte Vecchio einige Plätze auf der Top500-Liste nach oben klettern.

Sapphire Rapids soll auch Intels neue Advanced Matrix Extensions (AMX) bringen. Die hohe KI-Rechenleistung soll es ermöglichen, diese Xeons zum Training von KI-Algorithmen einzusetzen und nicht nur für deren Anwendung (Inferencing). Das ist eine Kampfansage an Nvidias A100 und die zahlreichen KI-Chip-Startups.

Dank PCIe 5.0 und CXL 1.1 sollen sich Rechenbeschleuniger besonders effizient mit Sapphire Rapids verzahnen lassen, vor allem eben Ponte Vecchio.

Ethernet statt Infiniband

Mit dem Zukauf von Barefoot Networks hat sich Intel leistungsstarke Tofino-2-Chips für Ethernet-Switches ins Haus geholt; Barefoot-Mitgründer Nick McKeown leitet nun sogar Intels neu geschaffene Network and Edge Group (NEX).

In Zukunft will Intel superschnelle Ethernet-Hostadapter und -Switches liefern, als günstigere Alternative zu Infiniband für Superrechner. Das ist eine weitere Volte in Intels Infiniband-Strategie: Intel hatte die Technik mit aus der Taufe gehoben, zog sich dann überraschend zurück, baute später wiederum eine zeitlang Infiniband als Omni Path Architecture (OPA) direkt in Xeons (F-Typen) ein und steigt nun anscheinend wieder aus.

(ciw)

Quelle: www.heise.de